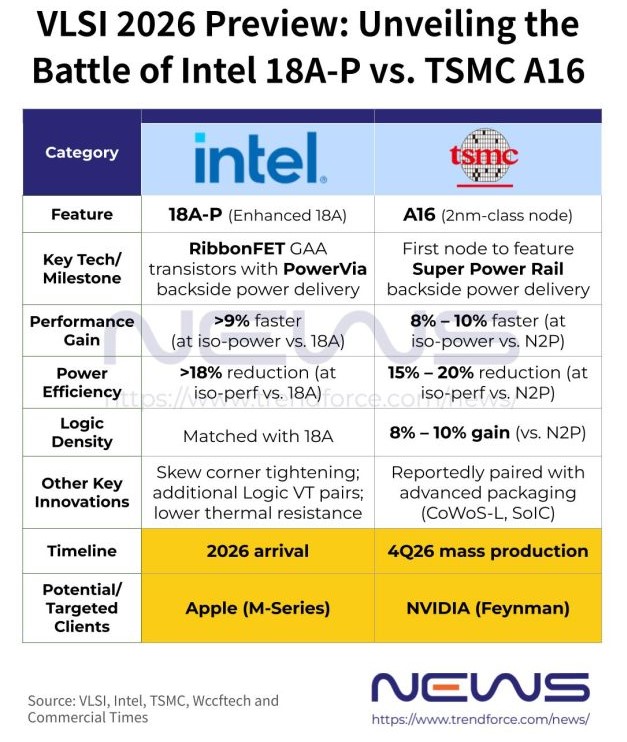

在此背景下,即將召開的VLSI研討會成為英特爾與台積電在先進製程技術領域競爭的主要舞台。台積電預計將在此次活動中展示其2奈米級A16埃CMOS技術。該製程使用環柵(GAA)電晶體,並透過新的「超級電源軌」(SPR)設計引入背面電力傳輸。

英特爾已經披露了其18A-P工藝的一些核心細節。據媒體報道,18A-P的關鍵結構參數,包括庫高度和接觸式多晶間距,與基線18A製程保持相同。主要升級集中在電晶體級調諧和電壓最佳化。VT BT 對選項的數量已從 18A 中的四個擴展到五個以上,並且在超低閾值電壓 (ULVT) 和低閾值電壓 (LVT) 之間添加了新的邏輯閾值電壓。

18A-P 製程還提高了製程可變性控制和熱效率,支援其低功耗和高效能目標。這些改進是蘋果和其他無晶圓廠晶片設計者對該技術表現出更大興趣的原因之一。為了實現這些效能提升,英特爾推出了基於其環柵架構的新 RibbonFET 變體,包括增強型接觸高效能電晶體和最佳化的低功耗元件,從而增強了裝置基礎,以實現更好的性能和能源效率。

英特爾還表示,已將 18A-P 製程的斜角收緊了 30%,旨在提高性能一致性並減少變異性。斜角是指同一製程節點內電晶體性能和功率特性的差異。隨著半導體製造朝向更激進的節點發展,電晶體的行為變得越來越不均勻,使得可變性控製成為主要挑戰。

據報道,英特爾首款基於 18A 製程的產品 Panther Lake 將於 2025 年底進入量產。該公司計劃分階段推出源自 18A 製程的製程技術,其中 18A-P 預計將於 2026 年上市,進一步升級的 18A-PT 製程計劃於 2028 年上市。

同時,台積電正在準備推出 A16 工藝,這是該公司第一個基於 Super Power Rail 技術的節點。該工藝將於6月14日至18日舉行的VLSI研討會上正式公佈。台積電錶示,與效能增強型N2P節點相比,A16在相同功耗下可達到8%至10%的效能提升,在相同效能下功耗降低15%至20%,並在晶片密度上提供額外8%至10%的增益。

台積電計畫於 2026 年第四季開始量產 A16。業界盛傳英偉達的 Feynman 晶片可能是第一個採用此製程的產品。供應鏈消息人士表示,A16 將與 CoWoS-L 和 SoIC 先進封裝技術搭配使用,使系統規模擴大至光罩尺寸的 9.5 倍。此流程主要針對高效能運算(HPC)工作負載。